Intel unveils ” Ponte Vecchio “: The GPU for future Exascale supercomputers

Built with 7-nanometer manufacturing technology, Foveros and chiplet design, the Ponte Vecchio GPU will be Intel’s parallel processing heart for Exascale Computing since 2021.

Intel has officially announced, at a press conference that anticipates the opening of the SC19 conference, the next generation of GPU of the Xe family which will debut from 2021.

The name is that of Ponte Vecchio already emerged in recent days, and is being confirmed the use of 7 nanometer production technology for its construction. This is the first architecture of the Xe family, specifically developed for the areas of use of Exascale-class supercomputers.

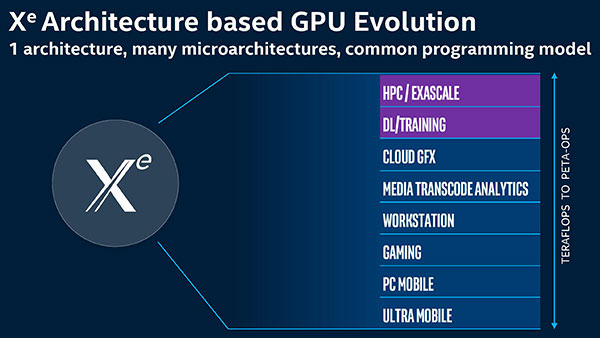

Intel Xe architecture will be declined by the American company within various types of products: the architectural base will be common, with the creation of different microarchitectures that adapt to the scenarios (workstation, gaming, cloud, mobile and ultramobile, etc. …) and a single programming model common to all solutions. For the moment Intel provides these 3 types of derivatives of the Xe architecture:

- Intel Xe LP : integrated and entry level GPU

- Intel Xe HP : gaming, enthusiast, datacenter and Artificial Intelligence

- Intel Xe HPC : Exascale solutions

Ponte Vecchio, in particular, is the name that identifies the first GPU of the Xe family intended for use in datacenters, belonging to the third family of Xe products. For Intel, it is the first product in this exascale class category, in which 7-nanometer production technology is combined, a design with chiplets (i.e. with small chips mounted on the same package and placed side by side) and Foveros technology for stacking of different dies one above the other.

The connection between the 16 chiplets that make up this solution will see the use of Intel Embedded Multi-Die Interconnect Bridge technology, while the CXL (Compute eXpress Link) interface will be used for communication between GPU and GPU. Intel has also reported the integration of a large cache for connecting the various GPU to each other, referred to as Rambo Cache and accessible from both the CPU and the GPU memory.

We know that Intel wants to maintain a unified approach to the programming model for its GPU architectures, through its own oneAPI initiative. In other words, allow developers to create applications and programs using a single approach and with them take advantage of the different hardware solutions developed by Intel according to the specific area of use.

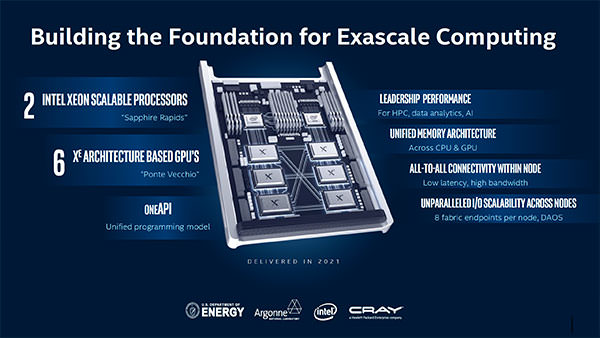

The first implementation of the Ponte Vecchio solution will take place in 2021 within the Aurora system, the supercomputer that will be installed inside the Argonne National Laboratory.

This system will consist of several nodes, each of which will integrate two Intel Xeon Scalable processors based on the ” Sapphire Rapids ” architecture and 6 GPUs of the Ponte Vecchio family, all interconnected with a unified memory architecture and using the unified oneAPI programming model.