PCI Express 6.0 runs fast

In a market where PCI Express 4.0 has not yet found widespread use, the group that deals with the PCI Express standard are running fast to ratify PCI Express 6.0 by 2021. The new specification has already reached version 0.5.

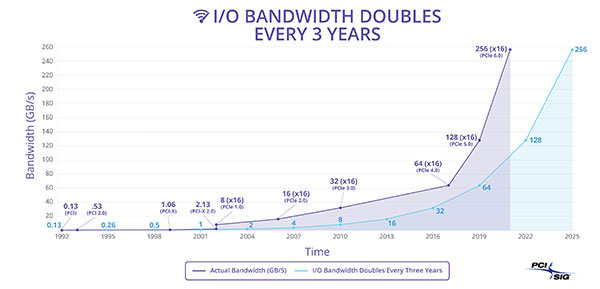

The PCI-SIG, the consortium that deals with the development of the PCI Express interconnection standard, has announced the achievement of version 0.5 of the PCI Express 6.0 specification, a new standard whose finalization is scheduled for 2021 and, which promises an increase in bandwidth eight times that of PCI Express 3.0, the most popular standard today.

Thanks to AMD and its X570 platform (remaining within the consumer platforms), the most advanced commercial version of the PCI Express available is 4.0, which guarantees a doubling of the bandwidth from 16 GB/s of PCIe 3.0 to 32 GB/s in a 16-line configuration (x16), a useful step forward, in the field of archiving than in that of video cards.

PCI Express 6.0 will see the maximum bandwidth jump to 128 GB/s (256 GB/s bidirectional), guaranteeing greater performance in the HPC sector, in that of artificial intelligence and machine learning.

Currently, Intel does not yet have consumer platforms compatible with PCIe 4.0, while for PCIe 5.0, the specification is complete and formally implementable. It is unclear what AMD will do in 2021 when it changes platforms by switching to a new socket (abandoning the long-lived AM4). The same goes for Intel.

The situation is different in the server sector, where the fourth generation ” Genoa ” AMD EPYC platform based on Zen 4 architecture should support PCIe 5.0, at least according to rumors. Intel itself is expected to adopt PCI Express 5.0 with Xeon solutions known by the codename Sapphire Rapids.

We cannot exclude more marked differences between the functionality of consumer and server platforms in the future, also in the face of the slow adoption of PCI Express 4.0 and the bandwidth requirements of the respective markets, with PCIe 4.0 that could long satisfy the needs of traditional computers.

As for PCI Express 6.0, the completion of the specification in 2021 does not mean that we will see compatible products immediately, but only that hardware manufacturers will be able to start developing solutions based on a definitive specification. The current version 0.5 is considered a first draft that covers all the key aspects of architecture and, which contains the first feedback from the manufacturers.

This step will be followed by version 0.7, to be considered as a ” complete draft, “with all the specifications defined and tested using a test chip. As of this version, the PCI-SIG no longer accepts the inclusion of new features.

Finally, we get to version 0.9, the final draft designed to allow consortium members to analyze the latest aspects given implementation. Then version 1.0 and the consequent public release are reached.

PCIe 6.0 remains backward compatible with previous versions but sees some changes to ensure greater speed. The most notable difference is the transition from Non-Return-to-Zero (NRZ) signaling technology with traditional two-level encoding (0 or 1) to Pulse-Amplitude Modulation 4 (PAM4) with four two-bit signal levels (00, 01, 10, 11).

This allows the transport of double the data without having to double the transmission bandwidth (and consequently, the operating frequency). Still, for this to be possible, it was necessary to guarantee the integrity of the signal by implementing for the first time in the standard a mechanism called Forward Error Correction (FEC). This solution causes the correction of error signals in a link to take place by providing a constant flow of data for error correction.